- 您现在的位置:买卖IC网 > Sheet目录364 > SST26VF032A-80-5I-S2AE (Microchip Technology)IC FLASH 32MBIT 8SOIC

�� �

�

�

�Serial� Quad� I/O� (SQI)� Flash� Memory�

�A� Microchip� Technology� Company�

�SST26VF016� /� SST26VF032�

�Data� Sheet�

�Reset� Quad� I/O� (RSTQIO)�

�The� Reset� Quad� I/O� instruction,� FFH,� resets� the� device� to� 1-bit� SPI� protocol� operation.� To� execute� a�

�Reset� Quad� I/O� operation,� the� host� drives� CE#� low,� sends� the� Reset� Quad� I/O� command� cycle� (FFH)�

�then,� drives� CE#� high.� The� device� accepts� either� SPI� (8� clocks)� or� SQI� (2� clocks)� command� cycles.� For�

�SPI,� SIO[3:1]� are� don’t� care� for� this� command,� but� should� be� driven� to� V� IH� or� V� IL� .�

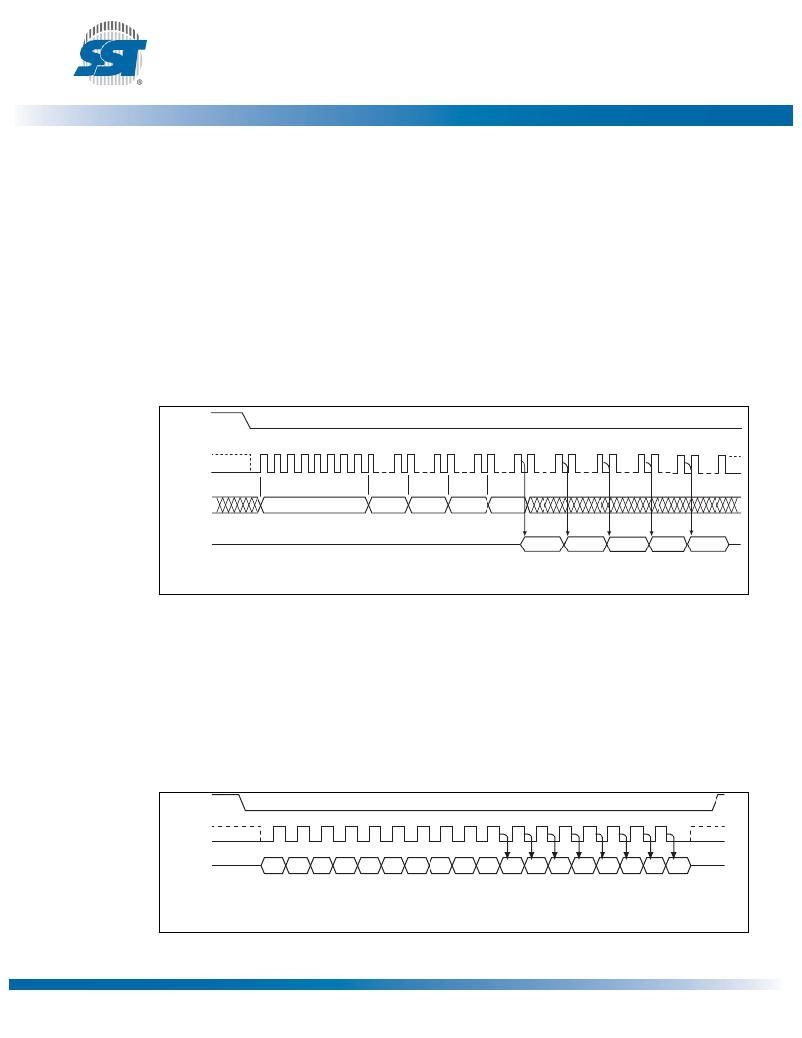

�High-Speed� Read� (80� MHz)�

�The� High-Speed� Read� instruction,� 0BH,� is� supported� in� both� SPI� bus� protocol� and� SQI� protocol.� On�

�power-up,� the� device� is� set� to� use� SPI.�

�Initiate� High-Speed� Read� by� executing� an� 8-bit� command,� 0BH,� followed� by� address� bits� [A23-A0]� and�

�a� dummy� byte.� CE#� must� remain� active� low� for� the� duration� of� the� High-Speed� Read� cycle.� SIO2� and�

�SIO3� must� be� driven� V� IH� for� the� duration� of� the� Read� cycle.� See� Figure� 10� for� the� High-Speed� Read�

�sequence� for� SPI� bus� protocol.�

�CE#�

�MODE� 3�

�0� 1� 2� 3� 4� 5� 6� 7� 8�

�15� 16�

�23� 24�

�31� 32�

�39� 40�

�47� 48�

�55� 56�

�63� 64�

�71� 72�

�80�

�SCK� MODE� 0�

�SI/SIO0�

�0B�

�ADD.�

�ADD.�

�ADD.�

�X�

�SO/SIO1�

�HIGH� IMPEDANCE�

�N�

�D� OUT�

�N+1�

�D� OUT�

�N+2�

�D� OUT�

�N+3�

�D� OUT�

�N+4�

�D� OUT�

�MSB�

�1359� F31.0�

�Note:� SIO2� and� SIO3� must� be� driven� V� IH�

�Figure� 10:� High-Speed� Read� Sequence� (SPI)�

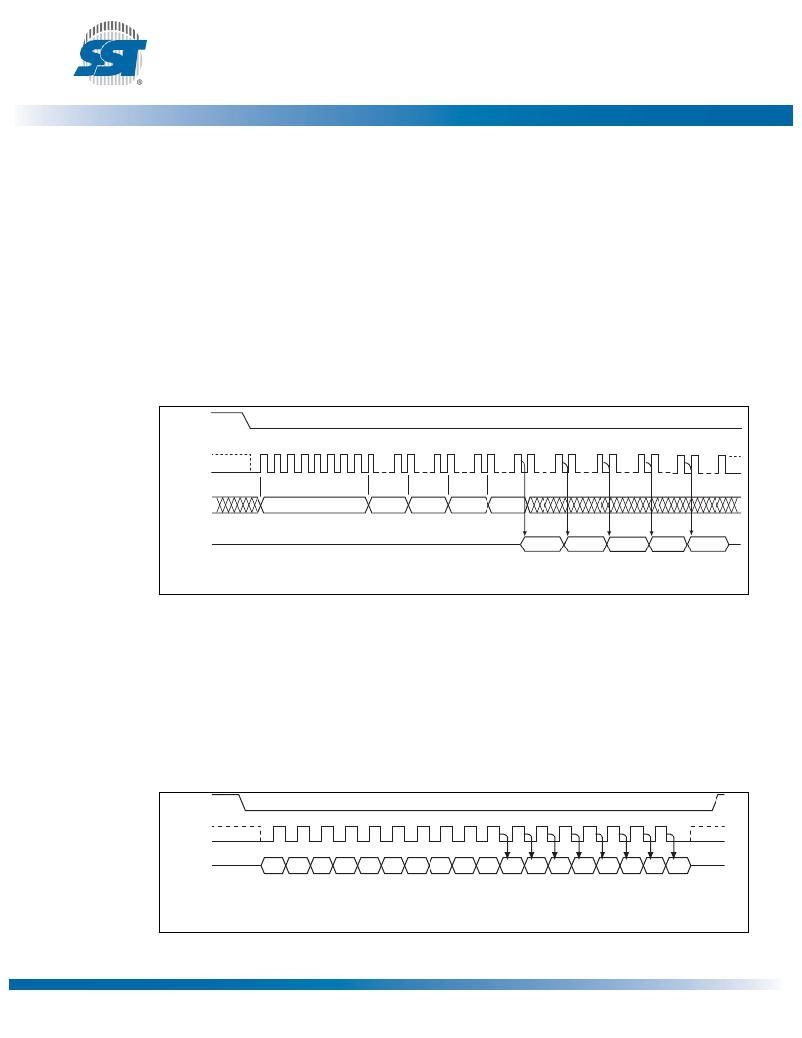

�In� SQI� protocol,� the� host� drives� CE#� low� then� send� the� Read� command� cycle� command,� 0BH,� followed� by�

�three� address� cycles� and� one� dummy� cycle.� Each� cycle� is� two� nibbles� (clocks)� long,� most� significant� nibble� first.�

�After� the� dummy� cycle,� the� Serial� Quad� I/O� (SQI)� Flash� Memory� outputs� data� on� the� falling� edge� of�

�the� SCK� signal� starting� from� the� specified� address� location.� The� device� continually� streams� data� out-�

�put� through� all� addresses� until� terminated� by� a� low-to-high� transition� on� CE#.� The� internal� address�

�pointer� automatically� increments� until� the� highest� memory� address� is� reached,� at� which� point� the�

�address� pointer� returns� to� address� location� 000000H.�

�During� this� operation,� blocks� that� are� Read-locked� will� output� data� 00H.�

�CE#�

�MODE� 3�

�0�

�1�

�2�

�9�

�16�

�MODE� 3�

�CLK�

�MODE� 0�

�MODE� 0�

�SIO(3:0)�

�C1� C0�

�A5�

�A4�

�A3�

�A2�

�A1�

�A0�

�X�

�X�

�H0�

�L0�

�H1�

�L1�

�H2�

�L2�

�H3�

�L3�

�MSB�

�Data� In�

�Note:� C[1:0]� =� 0BH�

�Figure� 11:� High-Speed� Read� Sequence� (SQI)�

�?2011� Silicon� Storage� Technology,� Inc.�

�15�

�Data� Out�

�DS-25017A�

�1359� F06.2�

�04/11�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SST38VF6402-90-5I-B3KE-T

IC FLASH MPF 64MBIT 90NS 48TFBGA

SST39LF802C-55-4C-MAQE-T

IC FLASH MPF 8MBIT 48-WFBGA

SST39SF040-70-4C-WHE

IC FLASH MPF 4MBIT 70NS 32TSOP

SST39VF1602C-70-4I-B3KE

IC FLASH MPF 16MBIT 70NS 48TFBGA

SST39VF200A-70-4I-MAQE

IC FLASH MPF 2MBIT 70NS 48-WFBGA

SST39VF3201-70-4I-B3KE-T

IC FLASH MPF 32MBIT 70NS 48TFBGA

SST39VF3201B-70-4C-B3KE

IC FLASH MPF 32MBIT 70NS 48TFBGA

SST39VF3201B-70-4I-EKE

IC FLASH MPF 32MBIT 70NS 48TSOP

相关代理商/技术参数

SST26VF064B

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:3.0V Serial Quad I/O (SQI) Flash Memory

SST26VF064B-104-5I-MF

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:3.0V Serial Quad I/O (SQI) Flash Memory

SST26VF064B-104-5I-SM

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:3.0V Serial Quad I/O (SQI) Flash Memory

SST26VF064B-104-5I-SO

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:3.0V Serial Quad I/O (SQI) Flash Memory

SST26VF064B-104-5I-TD

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:3.0V Serial Quad I/O (SQI) Flash Memory

SST26VF064B-104I/MF

制造商:Microchip Technology Inc 功能描述:3.0V SERIAL QUAD I/O (SQI) FLASH MEMORY - Rail/Tube

SST26VF064BA

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:3.0V Serial Quad I/O (SQI) Flash Memory

SST26VF064BA-104-5I-MF

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:3.0V Serial Quad I/O (SQI) Flash Memory